2. Alat dan Bahan

[Kembali]

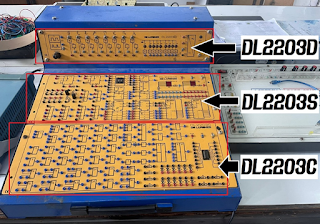

Alat dan bahan 1

Alat dan bahan 2

4. Prinsip Kerja [Kembali]

Pada percobaan terdapat rangkaian J-K flip flop disebelah kanan dan rangkaian D flip flop disebelah kiri. Dimana masing-masing terhubung ke saklar SW SPDT dengan salah satu pin saklar terhubung ke VCC yang kemudian dianggap berlogika 1 dan pin satunya lagi terhubung ke ground yang kemudian dianggap berlogika 0. Karena masing-masing inputan sudah memiliki ketentuan sesuai dengan kondisi yang tertera. Dapat dilihat masing R-S baik pada rangkaian J-k flip flop maupun rangkaian D flip flop berlogika 1 sedangkan memiliki kondisi aktif LOW sehingga R-S untuk kedua rangkaian tersebut tidak aktif. Pada J-K flip flop karena R-S tidak aktif yang artinya berada pada keadaan reset dengan input J = 0 dan K = 1 sehingga didapatkan output Q = 0 sessuai dengan tabel kebenaran. Pada D flip flop dengan tidak aktifnya R-S dan clock yang berada pada aktif HIGH. memasuakan inputan D dengan logika 1 ataupun 0 hasil output Q tetap akan berlogika 0 sesuai dengan tabel kebenaran

1. Bagaimana jika B0 dan B1 sama diberi logika 0, apa yang terjadi pada rangkaian

jawab :

B1 dan B0 terhubung dengan set dan riset, apabila B0 dan B1 diberi logika 0. Maka output Q dan Q komplemennya akan selalu berlogika 1 . Hal itu disebabkan karena B1 dan B0 aktif LOW yang akan aktif pada saat berlogika 0

2. Bagaimana jika B3 diputuskan atau tidak dihubungkan pada rangkaian apa yang terjadi pada rangkaian

jawab :

Ketika B3 berfungsi sebagai clock, jika diputuskan maka akibatnya pada rangkaian adalah tidak bisa terjadinya keadaan toggle, karena kondisi toggle memerlukan clock untuk melakukan perlawanan terhadap input.

3. Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang pada flip flop

jawab :

Kondisi toggle adalah suatu kondisi masukan yang mengakibatkan logika output (Q) berkebalikan dari kondisi sebelumnya saat dipicu dan terjadi secara terus-menerus

Kondisi not change adalah kondisi masukan yang membuat logika output (Q) sama seperti logika output keadaan sebelumnya

Kondisi terlarang adalah keadaan yang tidak diperbolehkan yaitu ketika output (Q) sama dengan Q komplemenya. Hal itu terjadi pada saat set dan riset sama-sama berlogika 1.

7. Link Download

[Kembali]

Download Rangkaian klik disini

Download Video klik disini

Download HTML klik disini

Download datasheet 75LS112 klik disini

Download datasheet 7474 klik disini

.jpg)

Tidak ada komentar:

Posting Komentar